Filtering

| V4L2 FPGA |

|---|

|

| Introduction |

| Getting the Code |

| Examples |

| GStreamer Pipelines |

| Supported Platforms |

| Contact Us |

Using faster processors for accelerating algorithms is not practical due to the high speeds involved in high power consumption. In order to minimize power consumption, hardware designers have moved to multi-processor systems to allow different applications to run in parallel.

FPGAs allow an even greater parallelization. They are capable of achieving a speed-up of more than 100x over an algorithm running on a single processor speed while spending less power. Moreover, the FPGA design makes it possible to replicate processing units as much as the communication and available area allow it.

RidgeRun Soft IP Cores are efficient in terms of speed and area consumption, which can meet hard real-time deadlines in the range of μs or ns with low latency, making the most of massive parallelism and low power consumption of FPGAs. These IP cores are fully compatible with the developed V4L2-FPGA driver. It avoids extra processing once the frame reaches the CPU, and also allows for customization of the parameters for the algorithms being executed in the FPGA, such as image width, height, format, offset, stride, and user custom fields.

Currently implemented algorithms

You can visit our complete catalog of IP cores for ISP in FPGA Image Signal Processor

Possible accelerated algorithms

- Edge enhancement

- Color correction

- White balancing

- Image denoising

- Image stitching

- Gamma correction

- Many others

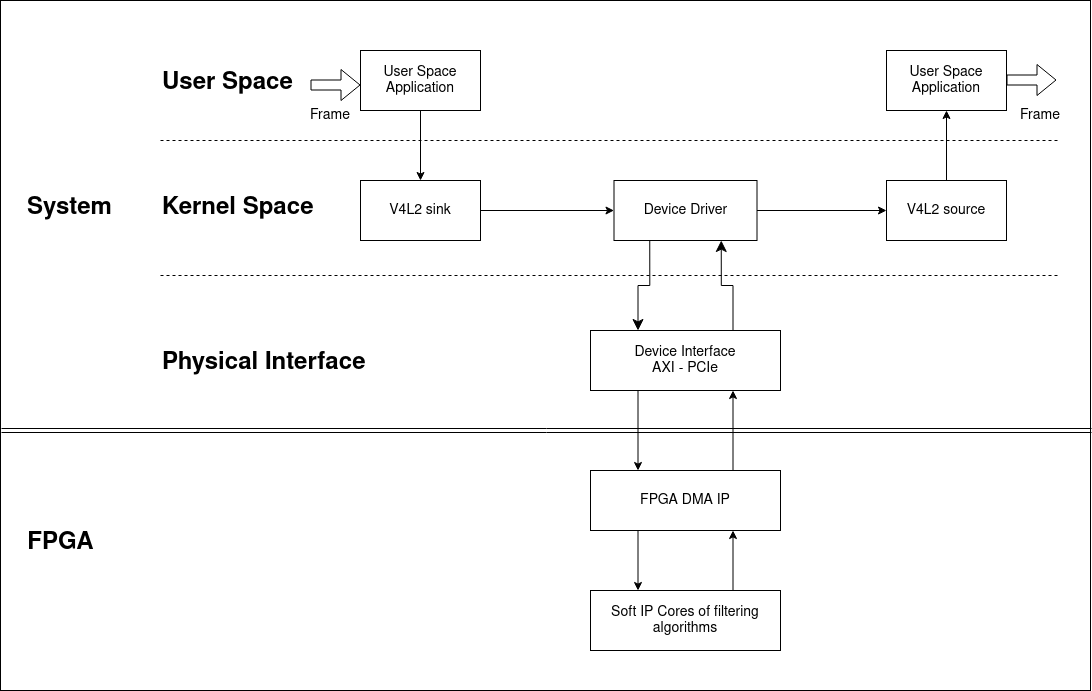

Topology

See also

https://www.intel.com/content/dam/altera-www/global/en_US/pdfs/literature/wp/wp-01029.pdf