V4L2 FPGA - Examples - Pass Through

| V4L2 FPGA |

|---|

|

| Introduction |

| Getting the Code |

| Examples |

| GStreamer Pipelines |

| Supported Platforms |

| Contact Us |

The Pass-Through accelerator serves as an example that guides in the hardware description by using the RidgeRun Wrapper for Vivado High-Level Synthesis (HLS) tool. For years, the hardware description on FPGA has been done by using Hardware Description Languages (HDL) such as VHDL or Verilog. The High-Level Synthesis comes as an alternative for easing the hardware description utilizing C/C++/SystemC as languages, which are commonly used in the software context. HLS makes it possible to describe complex algorithms easier, compared to doing it in Verilog or VHDL.

HLS uses a synthesizer for translating from High-Level languages to RTL. Behind your C/C++ code, the synthesizer configures Look-Up Tables (LUT), sets of registers (FIFO), blocks of memory (BRAM), muxes, and Digital Signal Processors (DSP, if available). C/C++ plays an interesting role when implementing algorithms, where these elements should be taken into account before starting the hardware description. For more information, you can visit: Xilinx Vivado HLS.

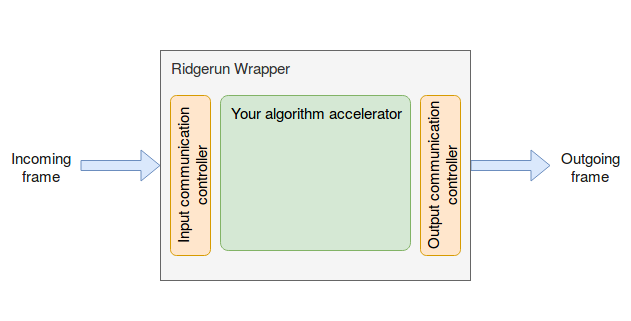

RidgeRun offers a framework, the RidgeRun Wrapper, to make the hardware description even much easier, without worry about how your accelerator is going to communicate with your system, see Figure 1. It is based on Vivado HLS and sets all the ports up in order to standardize the communication protocol, with optimum properties for image accelerators. Thus, hardware designers just have to concentrate on describing their algorithms instead of worrying about communication.

The Pass-Through accelerator also helps to illustrate which is the maximum performance achievable by your system, taking into account communication overhead, FPGA speed, and others. For the configuration presented in Table 1, the achieved results were as shown in Table 2.

| Resource | Description |

|---|---|

| Platform | Nvidia AGX Xavier |

| PCI-e | v2.0 - 1 lane |

| FPGA Board | PicoEVB |

| Resolution | Maximum framerate (fps) |

|---|---|

| 4k | 38.90 |

| 1080p | 144.5 |

| 720p | 294.729 |

According to Table 2, the maximum performance achievable by the hardware acceleration on a PicoEVB is 38.90 fps at a 4K resolution, which is sufficient for most image processing applications. The performance will lower depending on how optimal is the accelerator description and how complex is the algorithm. Also, the performance will depend on the power vs area trade-off. Boosting an application up in speed will also require more area.

Pass-Through I/O properties

The input/output images have limitations in format and size, which are indicated below:

| Property | Input image | Output image |

|---|---|---|

| Min width | 8 | 8 |

| Max width | 4096 | 4096 |

| Min height | 8 | 8 |

| Max height | 2160 | 2160 |

| Formats | 8-bit Gray (Mono) | 8-bit Gray (Mono) |