V4L2 FPGA - GStreamer Pipelines - Frame Grabber

| V4L2 FPGA |

|---|

|

| Introduction |

| Getting the Code |

| Examples |

| GStreamer Pipelines |

| Supported Platforms |

| Contact Us |

Overview

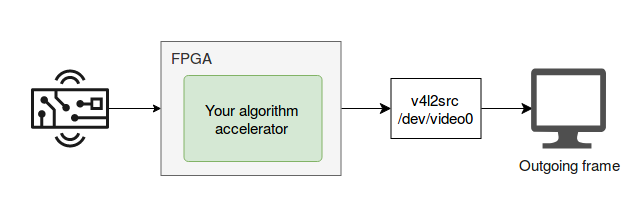

This wiki section describes how to use the V4L2-FPGA for communicating with a hardware accelerator, which generates a video pattern and sends it to the CPU. You can try using one of the following examples for performing these tests:

To use them, you need to configure your FPGA before running any of the pipelines shown below.

Basically, you can implement the pipeline illustrated in Figure 1 using GStreamer, which is performed in the following section.

The following pipelines generate a video pattern, sends it to the hardware accelerator implemented on the FPGA and retrieves the result.

Frame Grabber Pipeline

4k

WIDTH=", width=(int)3840" HEIGHT=", height=(int)2160" gst-launch-1.0 v4l2src device=/dev/video0 ! "video/x-raw $WIDTH $HEIGHT" ! videoconvert ! queue ! autovideosink-v

1080p

WIDTH=", width=(int)1920" HEIGHT=", height=(int)1080" gst-launch-1.0 v4l2src device=/dev/video0 ! "video/x-raw $WIDTH $HEIGHT" ! videoconvert ! queue ! autovideosink-v

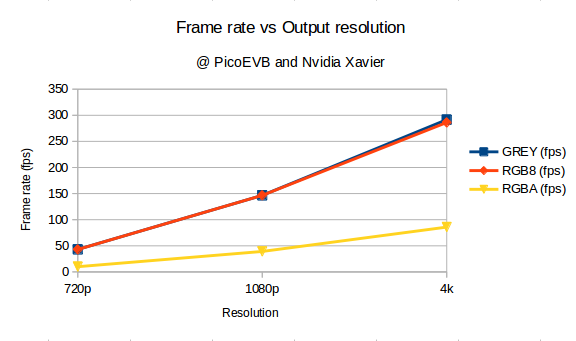

Performance

| Resolution | GREY (fps) | RGB8 (fps) | RGBA (fps) |

|---|---|---|---|

| 4k | 43.087 | 43.000 | 9.955 |

| 1080p | 146.636 | 146.600 | 39.180 |

| 720p | 291.598 | 286.218 | 85.810 |