Kria KV260

FPGA Minutes to Become an Expert RidgeRun documentation is currently under development. |

| FPGA Minutes to Become an Expert |

|---|

|

| Introduction |

| FPGA Knowledge |

|

Synthesis Flows

|

| Xilinx FPGAs |

|

Evaluation boards Development workflow and tools Getting Started |

| Lattice FPGAs |

|

Evaluation boards |

| Simulation Tools |

| CocoTB |

| AI and Machine Learning |

| Contact Us |

Introduction

Customize an existing capturing overlay

We are going to use the reference platforms repository and the kv260_ispMipiRx_vcu_DP platform as a base.

So let's clone the repo and make the xsa project!

git clone https://github.com/Xilinx/kria-vitis-platforms.git -b xlnx_rel_v2022.1 cd kria-vitis-platforms/kv260/platforms/vivado/kv260_ispMipiRx_vcu_DP make xsa

After the build process completes, lets open the generated output in ./project/kv260_ispMipiRx_vcu_DP.xpr with the vivado GUI.

As a recommendation, since the design is quite big, it might consume al resources, reducing the number of global threads can help with this. Go to Window-> tcl console and input this con the console: set_param general.maxthreads 2

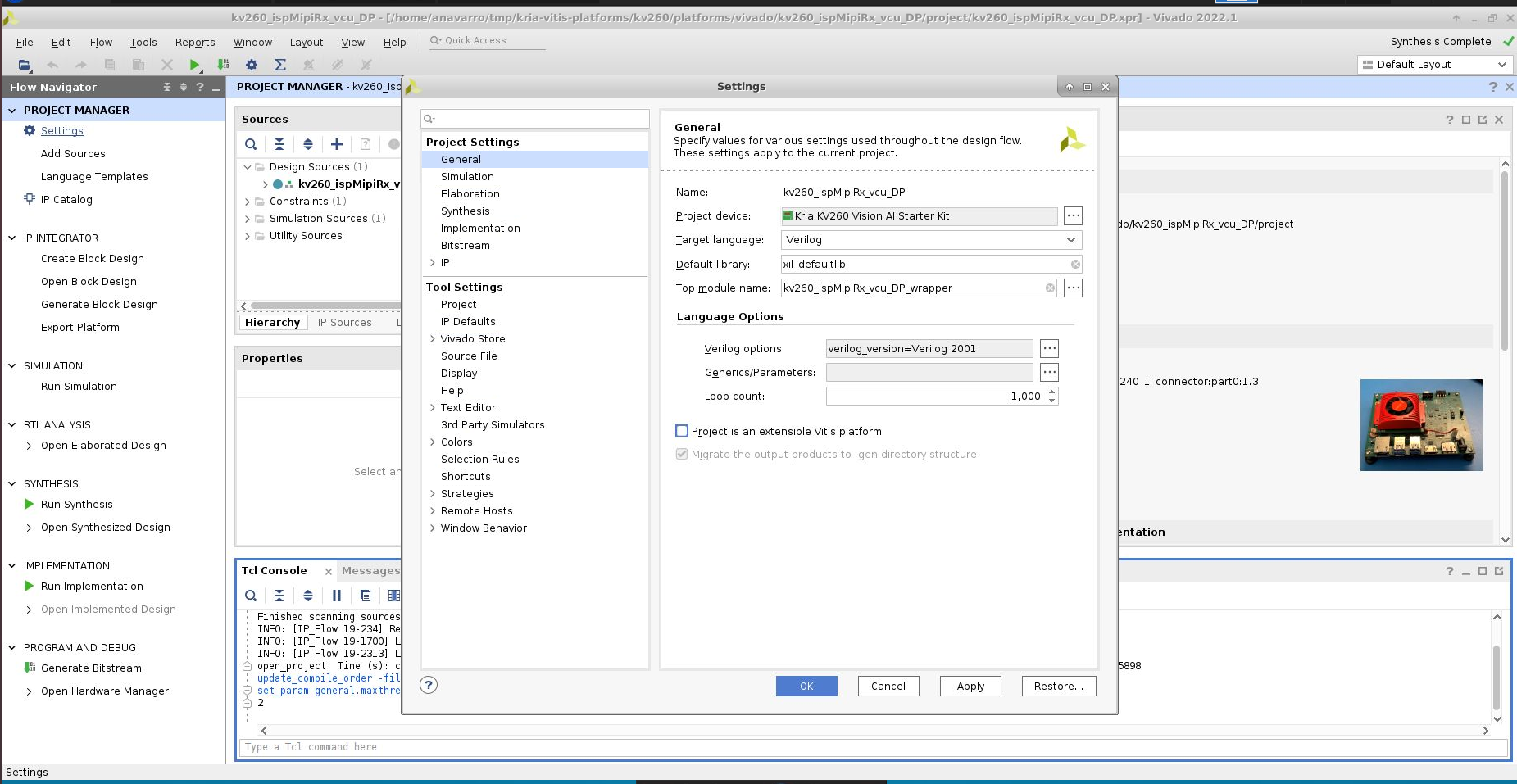

To be able to export the synthesized design we need to convert the project to a hardware project by disabling the vitis extensible platform. Go to Project Manager > Settings and in the General tab uncheck the box, the following image shows the window

RidgeRun Services

RidgeRun has expertise in offloading processing algorithms using FPGAs, from Image Signal Processing to AI offloading. Our services include:

- Algorithm Acceleration using FPGAs.

- Image Signal Processing IP Cores.

- Linux Device Drivers.

- Low Power AI Acceleration using FPGAs.

- Accelerated C++ Applications.

And it includes much more. Contact us at https://www.ridgerun.com/contact.