FPGA Image Signal Processor - FPGA ISP Accelerators - HistogramEqualizer

| FPGA Image Signal Processor |

|---|

|

| Introduction |

| FPGA ISP Accelerators/Modules |

| Getting the Code |

| Examples |

| GStreamer Pipelines |

| Tested Platforms |

| Contact Us |

Introduction

The FPGA-ISP Histogram Equalization Accelerator is an FPGA accelerator that performs the histogram equalization in grayscale (1 channel) images. With the histogram equalization, some features are highlighted with the equalization, given that the details are more notable thanks to the color equalization.

Supported caps

The FPGA-ISP Histogram Equalization Accelerator is capable of managing the following image properties:

Input

Min resolution: 8x8 Max resolution: 4096x2160 Formats: GRAY8 (8-bit Grayscale)

Output

Min resolution: 8x8 Max resolution: 4096x2160 (same as input) Formats: GRAY8 (8-bit Grayscale)

Algorithm overview

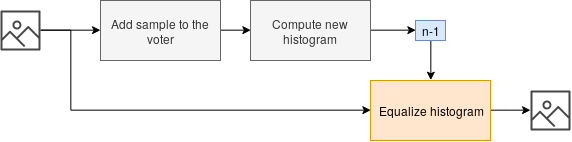

This accelerator uses an approximation to compute the histogram for color equalization. Given that the image is transmitted as a stream of pixels through a FIFO communication, the histogram computed for the first frame will serve as the reference for the following frame. Thus, the equalization is performed by using the histogram of the last image on the current. This approximation is valid for video sequences that not change noticeably from one frame to another, involving a framerate higher than 10.

The following diagram presents the algorithm used for the accelerator design. It illustrates how the equalizer uses the histogram computed with the frame n-1 on the frame n.

The following pictures depict an example given an input image and its output after being processed by the Histogram Equalization accelerator.

-

Input

-

Output

It is possible to see that some details are highlighted after equalizing the color histogram.

Example pipelines

In combination with RidgeRun's V4L2-FPGA, it is possible to create a V4L2 interface with GStreamer support, making even easier your computer vision application for embedded systems. Here is some example of pipelines to test the FPGA-ISP Histogram Equalizer.

Generator (Accelerator input)

gst-launch-1.0 videotestsrc ! video/x-raw,format=GRAY8,width=640,height=480 ! v4l2sink device=/dev/video2 -v

Sink (Accelerator output)

gst-launch-1.0 v4l2src device=/dev/video1 ! "video/x-raw, width=640, height=480,format=GRAY8" ! perf ! videoconvert ! xvimagesink

Benchmarks

| Resolution | Maximum framerate (fps) |

|---|---|

| 4k | 7,478 |

| 1080p | 29,510 |

| 720p | 64,830 |

These framerates are taken based on the following setup:

System: NVidia Jetson Xavier FPGA: PicoEVB (Artix 7 XC7A50T CSG325 -2l) OS: Ubuntu 18.04 PCI-e: v2.0 - 1 lane

You can reproduce these results by using the following pipelines:

Generator (Accelerator input)

gst-launch-1.0 videotestsrc ! video/x-raw,format=GRAY8,width=640,height=480 ! v4l2sink device=/dev/video2 -v

Sink (Accelerator output)

gst-launch-1.0 v4l2src device=/dev/video1 ! "video/x-raw, width=640, height=480,format=GRAY8" ! perf ! fakesink sync=false

Known issues

1. GStreamer autonegotiation: The caps, such as width, height, and format, must be specified in the pipeline.