V4L2 FPGA/Introduction: Difference between revisions

m (Add next link) |

(Adding section for PCIe, V4L2 and PicoEVB) |

||

| Line 6: | Line 6: | ||

--> | --> | ||

Modern systems require each day more complex algorithms, | Modern systems require each day more complex algorithms, with increasing complexity more powerful systems are needed. | ||

Some systems such as GPUs allow for acceleration might be prohibiting in terms of power and cost. FPGAs on the other hand allow for faster execution and better power efficiency at the cost of a longer development cycle and a harder integration into existing multimedia systems. V4L2 PCIe is project from Ridgerun Engineering which allows for easy integration of FPGA-based systems into multimedia systems such as GStreamer. | |||

=General concepts= | =General concepts= | ||

==Project Structure== | |||

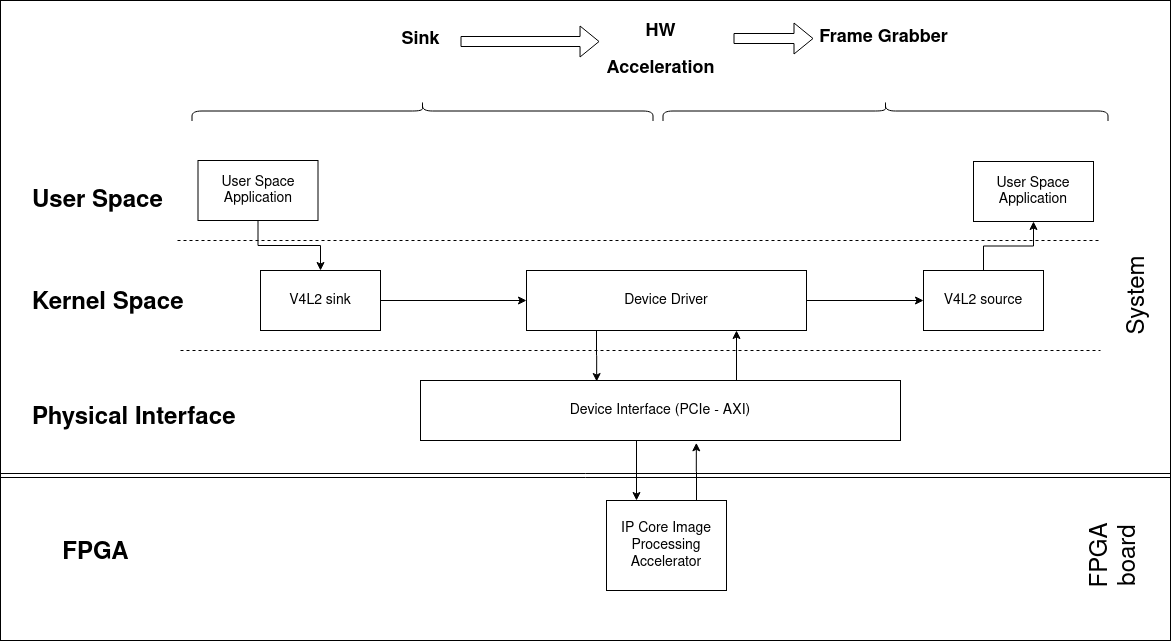

This project consists of three subsystems which allow for the acceleration of algorithms on custom hardware as shown in the following image: | This project consists of three subsystems which allow for the acceleration of algorithms on custom hardware as shown in the following image: | ||

| Line 21: | Line 23: | ||

==PCIe== | |||

PCI Express is a high-speed bus standard. PCIe slots can contain multiple lanes allowing for further speedup by transmitting information in each slot by parallel. It's the common interface for bandwidth for GPUs, Wi-Fi cards and SSDs. | |||

{| class="wikitable" | |||

|- | |||

! Version !! Bandwidth (per lane) !! Bandwidth (per lane in a 16x slot) | |||

|- | |||

| PCIe 1.0 || 2 Gbit/s || 32 Gbit/s | |||

|- | |||

| PCIe 2.0 || 4 Gbit/s || 64 Gbit/s | |||

|- | |||

| PCIe 3.0 || 7.877 Gbit/s || 126.032 Gbit/s | |||

|- | |||

| PCIe 4.0 || 15.752 Gbit/s || 252.032 Gbit/s | |||

|} | |||

PCIe compatible cards also come in a Mini Card factor which has a a more flexible physical specification to connect to the PCIe bus, one example of these cards is the PicoEVB board | |||

==V4L2== | |||

Video4Linux is a collection of drivers and an common API for supporting realtime video capture on Linux systems. | |||

The V4L2 provides a video capture interface to get video data from a tuner or camera device, a video output interface which can provide video images outside of the device. | |||

The API also implements code which enables applications to discover a given device's capabilities and to configure the device to operate in the desired manner. These include cropping, frame rates, video compression, image parameters, video formats, etc. | |||

==PicoEVB== | |||

The PicoEVB is a Artix-7 FPGA which fits into a M.2 key A or E slot. The Artix-7 FPGA provides 51 160 logic cells, 120 DSP48 slices, and 2,7Mbits de BRAM, it also provides 8 digital I/O, and 2 analog I/O. It has a built-in FTAG cable which works with Vivado and Labtools. | |||

{| class="wikitable" | |||

|- | |||

! Feature !! Specification | |||

|- | |||

| FPGA || Xilinx Artix 7 | |||

|- | |||

| Form Factor || M.2, A and E slots | |||

|- | |||

| Host Interface || PCIe 2.0 x1 | |||

|} | |||

=Further Reading= | |||

https://picoevb.com/ | |||

<noinclude> | <noinclude> | ||

{{V4L2_PCIe/Foot||Introduction/Frame Grabber}} | {{V4L2_PCIe/Foot||Introduction/Frame Grabber}} | ||

</noinclude> | </noinclude> | ||

Revision as of 17:29, 5 April 2019

This project is under development. |

Modern systems require each day more complex algorithms, with increasing complexity more powerful systems are needed.

Some systems such as GPUs allow for acceleration might be prohibiting in terms of power and cost. FPGAs on the other hand allow for faster execution and better power efficiency at the cost of a longer development cycle and a harder integration into existing multimedia systems. V4L2 PCIe is project from Ridgerun Engineering which allows for easy integration of FPGA-based systems into multimedia systems such as GStreamer.

General concepts

Project Structure

This project consists of three subsystems which allow for the acceleration of algorithms on custom hardware as shown in the following image:

Frame Sink: which allows the sending of video frames into a PCIe device, this can either be a display or a hardware accelerator such as shown in one shown in the image.

Frame Grabber: allows for the capture of frames from a PCIe device, this device can be either a camera or the result of a hardware accelerator.

HW accelerator: this subsystem allows for the processing of frames by complex algorithms, algorithms implemented in hardware are less power intensive, faster and allow for parallelism.

PCIe

PCI Express is a high-speed bus standard. PCIe slots can contain multiple lanes allowing for further speedup by transmitting information in each slot by parallel. It's the common interface for bandwidth for GPUs, Wi-Fi cards and SSDs.

| Version | Bandwidth (per lane) | Bandwidth (per lane in a 16x slot) |

|---|---|---|

| PCIe 1.0 | 2 Gbit/s | 32 Gbit/s |

| PCIe 2.0 | 4 Gbit/s | 64 Gbit/s |

| PCIe 3.0 | 7.877 Gbit/s | 126.032 Gbit/s |

| PCIe 4.0 | 15.752 Gbit/s | 252.032 Gbit/s |

PCIe compatible cards also come in a Mini Card factor which has a a more flexible physical specification to connect to the PCIe bus, one example of these cards is the PicoEVB board

V4L2

Video4Linux is a collection of drivers and an common API for supporting realtime video capture on Linux systems.

The V4L2 provides a video capture interface to get video data from a tuner or camera device, a video output interface which can provide video images outside of the device.

The API also implements code which enables applications to discover a given device's capabilities and to configure the device to operate in the desired manner. These include cropping, frame rates, video compression, image parameters, video formats, etc.

PicoEVB

The PicoEVB is a Artix-7 FPGA which fits into a M.2 key A or E slot. The Artix-7 FPGA provides 51 160 logic cells, 120 DSP48 slices, and 2,7Mbits de BRAM, it also provides 8 digital I/O, and 2 analog I/O. It has a built-in FTAG cable which works with Vivado and Labtools.

| Feature | Specification |

|---|---|

| FPGA | Xilinx Artix 7 |

| Form Factor | M.2, A and E slots |

| Host Interface | PCIe 2.0 x1 |

Further Reading